### **DAFTAR PUSTAKA**

- [1] K. Kaur, "Earthquake: its Causes, Types & Measurement," *Int. J. Sci. Res.*, vol. 4, no. 7, hal. 260–261, 2015.

- [2] W. Guo, Y. Hu, Y. Li, Z. Zhai, dan P. Shao, "Seismic performance evaluation of typical dampers designed by Chinese Code subjected to the main shock-aftershocks," *Soil Dyn. Earthq. Eng.*, vol. 126, no. August 2018, hal. 105829, Nov 2019.

- [3] M. Anda, S. Purwanto, E. Suryani, Husnain, dan Muchtar, "Pristine Soil property and Mineralogy as The Strategic Rehabilitation Basis in Post-Earthquake-Induced Liquefaction, Tsunami and Landslide in Palu, Indonesia," *CATENA*, vol. 203, hal. 105345, Agu 2021.

- [4] J. O. Oluwafemi, O. M. Ofuyatan, O. M. Sadiq, S. O. Oyebisi, J. S. Abolarin, dan K. O. Babaremu, "Review of World Earthquakes," *Int. J. Civ. Eng. Technol.*, vol. 9, no. 9, hal. 440–464, 2018.

- [5] M. A. Khan, *Earthquake-Resistant Structures*, 1st ed. London: Elsevier Inc., 2013.

- [6] Y. Zhou, H. Shao, Y. Cao, dan E. M. Lui, "Application of buckling-restrained braces to earthquake-resistant design of buildings: A review," *Eng. Struct.*, vol. 246, no. April 2020, hal. 112991, Nov 2021.

- [7] W. Guo, P. Shao, H. Li, Y. Long, dan J. Mao, "Accuracy Assessment of Shake Table Device on Strong Earthquake Output," *Adv. Civ. Eng.*, vol. 2019, hal. 1–23, Nov 2019.

- [8] H. Damerji, S. Yadav, Y. Sieffert, L. Debove, F. Vieux-Champagne, dan Y. Malecot, "Design of a Shake Table with Moderate Cost," *Exp. Tech.*, Jun 2021.

- [9] W. Guo, Z. Zhai, Y. Cui, Z. Yu, dan X. Wu, "Seismic performance assessment of low-rise precast wall panel structure with bolt connections," *Eng. Struct.*, vol. 181, no. November 2018, hal. 562–578, Feb 2019.

- [10] W. Guo, C. Zeng, H. Gou, Y. Hu, H. Xu, dan L. Guo, "Rotational Friction Damper's Performance for Controlling Seismic Response of High Speed Railway Bridge-Track System," *Comput. Model. Eng. Sci.*, vol. 120, no. 3, hal. 491–515, 2019.

- [11] A. R. Plummer, "Model-based Motion Control for Multi-Axis Servo Hydraulic Shaking Tables," *Control Eng. Pract.*, vol. 53, hal. 109–122, Agu 2016.

- [12] T. Y. Yang, K. Li, J. Y. Lin, Y. Li, dan D. P. Tung, "Development of high-performance shake tables using the hierarchical control strategy and nonlinear control techniques," *Earthq. Eng. Struct. Dyn.*, vol. 44, no. 11, hal. 1717–1728, Sep 2015.

- [13] D. Suryadi, H. Syamitra, A. Fauzan, N. Darath, dan I. Agustian, "Meja

- Getar dengan Sistem Tiga Penggerak Pneumatik untuk Skala Laboratorium," *Met. J. Sist. Mek. dan Termal*, vol. 5, no. 1, hal. 44–50, 2021.

- [14] E. Damcı dan Ç. Şekerci, "Development of a Low-Cost Single-Axis Shake Table Based on Arduino," *Exp. Tech.*, vol. 43, no. 2, hal. 179–198, Apr 2019.

- [15] K. bin Ngadimon, "Design and Simulation of Hydraulic Shaking Table," University of Technology Malaysia, 2006.

- [16] K. P. Ryu dan A. M. Reinhorn, "Real-time control of shake tables for nonlinear hysteretic systems," *Struct. Control Heal. Monit.*, vol. 24, no. 2, hal. e1871, Feb 2017.

- [17] R. T. Severn, "The Development of Shaking Tables–A Historical Note," *Earthq. Eng. Struct. Dyn.*, vol. 40, hal. 195–213, 2011.

- [18] N. Nakata, "Acceleration trajectory tracking control for earthquake simulators," *Eng. Struct.*, vol. 32, no. 8, hal. 2229–2236, 2010.

- [19] T. L. Trombetti dan J. P. Conte, "Shaking Table Dynamics: Results from a Test-Analysis Comparison Study," *J. Earthq. Eng.*, vol. 6, no. 4, hal. 513–551, Okt 2002.

- [20] W. Bolton, *Mechatronics, ElEctronic Control Systems in Mechanical and Electrical Engineering*, Sixth. United Kingdom: Pearson Education Limited, 2015.

- [21] Syahrul, *Pemrograman Mikrokontroler AVR dengan Bahasa Assembly dan C.* Bandung: Penerbit Informatika, 2014.

- [22] "Arduino-Home." [Daring]. Tersedia pada: www.arduino.cc. [Diakses: 04-Mei-2021].

- [23] R. H. Bishop, *The Mechatronics Handbook*. New York: CRC Press, 2002.

- [24] R. B. Walters, *Hydraulic and Electric-Hydraulic Control Systems*, 2 ed. Wembley: Springer, Dordrecht, 2000.

- [25] N. D. Manring dan R. C. Fales, *Hydraulic Control Systems*, 2nd ed. West Sussex: Wiley, 2020.

- [26] J. Fraden, *Handbook of Modern Sensors*, 5th ed. Switzerland: Springer International Publishing, 2016.

- [27] "ADXL345-Analog Devices." [Daring]. Tersedia pada: https://www.analog.com/.

- [28] I. Setiawan, *Kontrol PID untuk Proses Industri*. Jakarta: PT. Elex Media Komputindo, 2008.

- [29] K. Ogata, *Modern Control Engineering*, 5th ed. New Jersey: Prentice Hall, 2010.

- [30] T. W. D. Hartanto dan Y. W. A. Prasetyo, *Analisis dan Desain Sistem Kontrol dengan MATLAB*. Yogyakarta: Andi, 2004.

# **LAMPIRAN**

# Lampiran A Data Hidrolik

| Motor             | AC, 3-phase                               |

|-------------------|-------------------------------------------|

| Daya Nominal      | 2,2 kW                                    |

| Tegangan Nominal  | 380 V                                     |

| Arus Nominal      | 5.1 A                                     |

| Frekuensi         | 50 Hz                                     |

| Kecepatan Nominal | 1420                                      |

| Standar Proteksi  | IP55                                      |

| Berat             | 19,8 kg                                   |

| Aktuasi           | Manual via VFD (variable frequency drive) |

# Lampiran B Spesifikasi pressure relief valve

| Fluida Hidrolik | Mineral Oil (disarankan) |  |

|-----------------|--------------------------|--|

| Tekanan Operasi | 50 bar                   |  |

| Metode Aktuasi  | Elektrik (On-off)        |  |

# Lampiran C Spesifikasi Solenoid Valve

| Aktuasi      | Solenoid Valve |

|--------------|----------------|

| Tegangan     | 24 VDC         |

| Arus Nominal | 800 mA         |

# Lampiran D Spesifikasi Silinder Hidrolik

| Silinder Hidrolik |                       |

|-------------------|-----------------------|

| Stroke            | 300 mm                |

| Fluida Hidrolik   | mineral oil           |

| Luas Area Tekan   | 12.56 cm <sup>2</sup> |

| Sensor HC SR04    |                       |

| Suplai tegangan   | 5 VDC                 |

| Arus              | 15 mA                 |

| Range             | 2 cm – 4 m            |

| Dimensi           | 45 X 20 X 15 mm       |

Lampiran E Spesifikasi Arduino Mega2560 dan Driver Mosfet

| Arduino Mega2560             |                   |

|------------------------------|-------------------|

| Tegangan Operasi             | 5V                |

| Input Tegangan (dianjurkan)  | 7-12V             |

| Input Tegangan (batas)       | 6-20V             |

| Digital I/O Pin              | 14 (6 output pwm) |

| Pin Masukan Analog           | 6                 |

| DC Current per I/O Pin       | 20 mA             |

| Driver Mosfet                |                   |

| Max Control Voltage (signal) | 6 V               |

| Chipset                      | IRF540            |

| Max Switch Current           | 10 A              |

| Max Switch Voltage           | 100V              |

Tech Support: services@elecfreaks.com

# **Ultrasonic Ranging Module HC - SR04**

## □ Product features:

Ultrasonic ranging module HC - SR04 provides 2cm - 400cm noncontact measurement function, the ranging accuracy can reach to 3mm. The modules includes ultrasonic transmitters, receiver and control circuit. The basic principle of work:

- (1) Using IO trigger for at least 10us high level signal,

- (2) The Module automatically sends eight 40 kHz and detect whether there is a pulse signal back.

- (3) IF the signal back, through high level, time of high output IO duration is the time from sending ultrasonic to returning. Test distance = (high level time $\times$ velocity of sound (340M/S) / 2,

# ☐ Wire connecting direct as following:

5V Supply

Trigger Pulse Input

Echo Pulse Output

**0V** Ground

### **Electric Parameter**

| Working Voltage   | DC 5 V |

|-------------------|--------|

| Working Current   | 15mA   |

| Working Frequency | 40Hz   |

| Max Range         | 4m     |

| Min Range            | 2cm                            |

|----------------------|--------------------------------|

| MeasuringAngle       | 15 degree                      |

| Trigger Input Signal | 10uS TTL pulse                 |

| Echo Output Signal   | Input TTL lever signal and the |

|                      | range in                       |

| Dimension            | 45*20*15mm                     |

# **Timing diagram**

The Timing diagram is shown below. You only need to supply a short 10uS pulse to the trigger input to start the ranging, and then the module will send out an 8 cycle burst of ultrasound at 40 kHz and raise its echo. The Echo is a distance object that is pulse width and the range in proportion .You can

calculate the range through the time interval between sending trigger signal and receiving echo signal. Formula: uS / 58 = centimeters or uS / 148 = inch; or: the range = high level time \* velocity (340M/S) / 2; we suggest to use over 60ms measurement cycle, in order to prevent trigger signal to the echo signal.

# ☐ Attention:

- The module is not suggested to connect directly to electric, if connected electric, the GND terminal should be connected the module first, otherwise, it will affect the normal work of the module.

- When tested objects, the range of area is not less than 0.5 square meters and the plane requests as smooth as possible, otherwise, it will affect the results of measuring.

www.Elecfreas.com

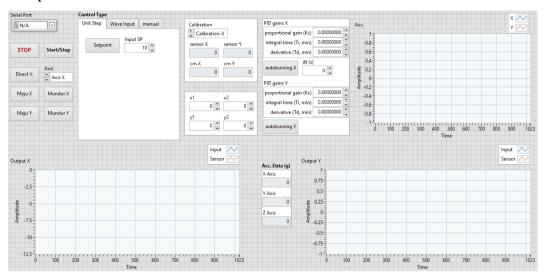

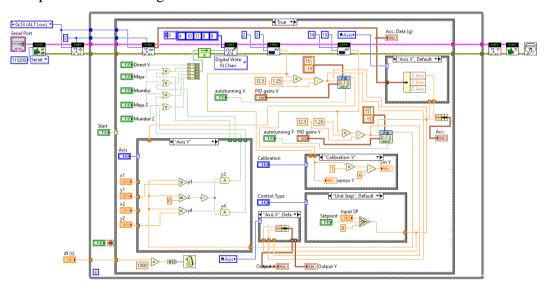

# Lampiran G Front Panel Labview

# Lampiran H Block Diagram Labview

# 3-Axis, $\pm 2$ g/ $\pm 4$ g/ $\pm 8$ g/ $\pm 16$ g Digital Accelerometer

ADXL345

### **FEATURES**

Ultralow power: as low as 40  $\mu A$  in measurement mode and 0.1  $\mu A$  in standby mode at  $V_S = 2.5 \, V$  (typical)

Power consumption scales automatically with bandwidth User-selectable resolution

Fixed 10-bit resolution

Full resolution, where resolution increases with g range, up to 13-bit resolution at ±16 g (maintaining 4 mg/LSB scale factor in all g ranges)

Embedded, patent pending FIFO technology minimizes host

Tap/double tap detection

Activity/inactivity monitoring

Free-fall detection

Supply voltage range: 2.0 V to 3.6 V

I/O voltage range: 1.7 V to V<sub>S</sub>

SPI (3- and 4-wire) and I<sup>2</sup>C digital interfaces

Flexible interrupt modes mappable to either interrupt pin Measurement ranges selectable via serial command

Bandwidth selectable via serial command

Wide temperature range (-40°C to +85°C)

10,000 a shock survival

Pb free/RoHS compliant

Small and thin:  $3 \text{ mm} \times 5 \text{ mm} \times 1 \text{ mm}$  LGA package

### **APPLICATIONS**

Handsets

Medical instrumentation

Gaming and pointing devices

Industrial instrumentation

Personal navigation devices

Hard disk drive (HDD) protection

Fitness equipment

### GENERAL DESCRIPTION

The ADXL345 is a small, thin, low power, 3-axis accelerometer with high resolution (13-bit) measurement at up to ±16 g. Digital output data is formatted as 16-bit twos complement and is accessible through either a SPI (3- or 4-wire) or I<sup>2</sup>C digital interface.

The ADXL345 is well suited for mobile device applications. It measures the static acceleration of gravity in tilt-sensing applications, as well as dynamic acceleration resulting from motion or shock. Its high resolution (4 mg/LSB) enables measurement of inclination changes less than 1.0°.

Several special sensing functions are provided. Activity and inactivity sensing detect the presence or lack of motion and if the acceleration on any axis exceeds a user-set level. Tap sensing detects single and double taps. Free-fall sensing detects if the device is falling. These functions can be mapped to one of two interrupt output pins. An integrated, patent pending 32-level first in, first out (FIFO) buffer can be used to store data to minimize host processor intervention.

Low power modes enable intelligent motion-based power management with threshold sensing and active acceleration measurement at extremely low power dissipation.

The ADXL345 is supplied in a small, thin, 3 mm  $\times$  5 mm  $\times$  1 mm, 14-lead, plastic package.

# FUNCTIONAL BLOCK DIAGRAM Vs. Vob 10 ADXL345 POWER AND CONTROL INTERCUPT I

# Figure 1. Rev. 0 Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use nor for any infringements of patents or other rights of third-parts between years from as use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and readseard trademarks and the procedure of their respective owners. See the last

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329,4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

### **SPECIFICATIONS**

$T_{A}=25^{o}C,\ V_{S}=2.5\ V,\ V_{DD\ UO}=1.8\ V,\ acceleration=0\ g,\ C_{S}=1\ \mu F\ tantalum,\ C_{IO}=0.1\ \mu F,\ unless\ otherwise\ noted.$

Table 1. Specifications<sup>1</sup>

| Parameter                                       | Test Conditions                                                                  | Min   | Тур           | Max   | Unit   |

|-------------------------------------------------|----------------------------------------------------------------------------------|-------|---------------|-------|--------|

| SENSOR INPUT                                    | Each axis                                                                        |       |               |       |        |

| Measurement Range                               | User selectable                                                                  |       | ±2, ±4, ±8, ± | 16    | g      |

| Nonlinearity                                    | Percentage of full scale                                                         |       | ±0.5          |       | 96     |

| Inter-Axis Alignment Error                      |                                                                                  |       | ±0.1          |       | Degree |

| Cross-Axis Sensitivity <sup>2</sup>             |                                                                                  |       | ±1            |       | 96     |

| OUTPUT RESOLUTION                               | Each axis                                                                        |       | 1000          |       |        |

| All g Ranges                                    | 10-bit resolution                                                                |       | 10            |       | Bits   |

| ±2 g Range                                      | Full resolution                                                                  |       | 10            |       | Bits   |

| ±4g Range                                       | Full resolution                                                                  |       | 11            |       | Bits   |

| ±8 g Range                                      | Full resolution                                                                  |       | 12            |       | Bits   |

| ±16 g Range                                     | Full resolution                                                                  |       | 13            |       | Bits   |

| SENSITIVITY                                     | Each axis                                                                        | -     | 10            |       | Dies   |

| Sensitivity at Xour, Your, Zour                 | $\pm 2 q$ , 10-bit or full resolution                                            | 232   | 256           | 286   | LSB/q  |

| Scale Factor at Xout, Yout, Zout                | ±2 g, 10-bit of full resolution                                                  | 3.5   | 3.9           | 4.3   | mg/LS  |

| Sensitivity at Xout, Yout, Zout                 | ±4 g, 10-bit resolution                                                          | 116   | 128           | 143   | LSB/g  |

| Scale Factor at Xout, Yout, Zout                | ±4 a, 10-bit resolution                                                          | 7.0   | 7.8           | 8.6   | mg/LS  |

|                                                 | ±8 a 10-bit resolution                                                           | 58    | 64            | 71    | LSB/a  |

| Sensitivity at Xour, Your, Zour                 |                                                                                  |       |               |       | -      |

| Scale Factor at Xout, Yout, Zout                | ±8 g, 10-bit resolution                                                          | 14.0  | 15.6          | 17.2  | mg/LS  |

| Sensitivity at Xout, Yout, Zout                 | $\pm 16 g$ , 10-bit resolution                                                   | 29    | 32            | 36    | LSB/g  |

| Scale Factor at Xour, Your, Zour                | ±16 g, 10-bit resolution                                                         | 28.1  | 31.2          | 34.3  | mg/LS  |

| Sensitivity Change Due to Temperature           |                                                                                  |       | ±0.01         |       | %/°C   |

| 0 g BIAS LEVEL                                  | Each axis                                                                        | 4000  |               |       |        |

| 0 g Output for Холт, Yолт                       |                                                                                  | -150  | ±40           | +150  | mg     |

| 0 g Output for Zout                             |                                                                                  | -250  | ±80           | +250  | mg     |

| 0 g Offset vs. Temperature for x-, y-Axes       |                                                                                  |       | ±0.8          |       | mg/°C  |

| 0 g Offset vs. Temperature for z-Axis           |                                                                                  |       | ±4.5          |       | mg/°C  |

| NOISE PERFORMANCE                               |                                                                                  |       |               |       |        |

| Noise (x-, y-Axes)                              | Data rate = $100 \text{ Hz}$ for $\pm 2 g$ , $10 \text{-bit}$ or full resolution |       | <1.0          |       | LSB rm |

| Noise (z-Axis)                                  | Data rate = $100 \text{ Hz}$ for $\pm 2 g$ , $10 \text{-bit}$ or full resolution |       | <1.5          |       | LSB rm |

| OUTPUT DATA RATE AND BANDWIDTH                  | User selectable                                                                  |       |               |       |        |

| Measurement Rate <sup>3</sup>                   |                                                                                  | 6.25  |               | 3200  | Hz     |

| SELF-TEST <sup>4</sup>                          | Data rate ≥ 100 Hz, 2.0 V ≤ V <sub>S</sub> ≤ 3.6 V                               |       |               |       |        |

| Output Change in x-Axis                         |                                                                                  | 0,20  |               | 2.10  | g      |

| Output Change in y-Axis                         |                                                                                  | -2.10 |               | -0.20 | q      |

| Output Change in z-Axis                         |                                                                                  | 0.30  |               | 3,40  | g      |

| POWER SUPPLY                                    |                                                                                  |       |               | 2010  | - 1    |

| Operating Voltage Range (Vs)                    |                                                                                  | 2,0   | 2.5           | 3.6   | V      |

| Interface Voltage Range (Vppvo)                 | V <sub>5</sub> ≤ 2.5 V                                                           | 1.7   | 1.8           | Vs    | ĺv     |

| interface voltage hange (volue)                 | V <sub>5</sub> ≥ 2.5 V                                                           | 2.0   | 2.5           | Vs    | l v    |

| Supply Current                                  | Data rate > 100 Hz                                                               | 2.0   | 145           | *3    | μA     |

| зарру саненс                                    | Data rate < 10 Hz                                                                |       | 40            |       | μA     |

| Standby Mode Leakage Current                    | Data late C 10112                                                                |       | 0.1           | 2     | μA     |

| Turn-On Time <sup>5</sup>                       | Data rate = 3200 Hz                                                              |       | 1.4           | 2     | ms     |

| #5450 (#545 #545 #545 #55 #55 #55 #55 #55 #55 # | Data late - 3200 FIZ                                                             | -     | 124           |       | IIIS   |

| TEMPERATURE                                     |                                                                                  | 40    |               | . 05  | 0.0    |

| Operating Temperature Range                     | +                                                                                | -40   |               | +85   | °C     |

| WEIGHT                                          |                                                                                  |       |               |       | 200000 |

| Device Weight                                   |                                                                                  |       | 20            |       | mg     |

<sup>1</sup> All minimum and maximum specifications are guaranteed. Typical specifications are not guaranteed.

2 Cross-axis sensitivity is defined as coupling between any two axes.

3 and admixed in shalf the output data rate.

4 Self-test change is defined as the output (g) when the SELF\_TEST bit = 1 (in the DATA\_FORMAT register) minus the output (g) when the SELF\_TEST bit = 0 (in the DATA\_FORMAT register). Due to device filtering, the output reaches its final value after 4 × τ when enabling or disabling self-test, where τ = 1/(data rate).

5 Turn-on and wake-up times are determined by the user-defined bandwidth. At a 100 Hz data rate, the turn-on and wake-up times are each approximately 11.1 ms. For other data rates, the turn-on and wake-up times are each approximately τ + 1.1 in milliseconds, where τ = 1/(data rate).

### ABSOLUTE MAXIMUM RATINGS

### Table 2

| Param eter                                           | Rating                                                              |

|------------------------------------------------------|---------------------------------------------------------------------|

| Acceleration                                         |                                                                     |

| Any Axis, Unpowered                                  | 10,000 g                                                            |

| Any Axis, Powered                                    | 10,000 g                                                            |

| <b>V</b> s                                           | -0.3 V to +3.6 V                                                    |

| V <sub>DD V</sub> O                                  | -0.3 V to +3.6 V                                                    |

| Digital Pins                                         | -0.3 V to V <sub>DD VO</sub> + 0.3 V or<br>3.6 V, whichever is less |

| All Other Pins                                       | -0.3 V to +3.6 V                                                    |

| Output Short-Circuit Duration<br>(Any Pin to Ground) | Indefinite                                                          |

| Temperature Range                                    |                                                                     |

| Powered                                              | -40°C to +105°C                                                     |

| Storage                                              | -40°C to +105°C                                                     |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

Table 3. Package Characteristics

| Package Type θ <sub>JA</sub> θ <sub>JC</sub> |         | Ι Δ         | Device Weight |

|----------------------------------------------|---------|-------------|---------------|

| Раскаде туре                                 | OJA     | <b>O</b> JC | Device Weight |

| 14-Terminal LGA                              | 150°C/W | 85°C/W      | 20 mg         |

### **ESD CAUTION**

CIN ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

ADXL345

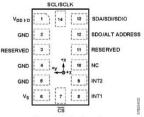

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ADXL345 TOP VIEW (Not to Scale) SCL/SCLK

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

| Pin No. | Mnemonic        | Description                                                                                             |

|---------|-----------------|---------------------------------------------------------------------------------------------------------|

| 1       | <b>V</b> DD I/O | Digital Interface Supply Voltage.                                                                       |

| 2       | GND             | Must be connected to ground.                                                                            |

| 3       | Reserved        | Reserved. This pin must be connected to V₃ or left open.                                                |

| 4       | GND             | Must be connected to ground.                                                                            |

| 5       | GND             | Must be connected to ground.                                                                            |

| 6       | Vs              | Supply Voltage.                                                                                         |

| 7       | <u>cs</u>       | Chip Select.                                                                                            |

| 8       | INT1            | Interrupt 1 Output.                                                                                     |

| 9       | INT2            | Interrupt 2 Output.                                                                                     |

| 10      | NC              | Not Internally Connected.                                                                               |

| 11      | Reserved        | Reserved. This pin must be connected to ground or left open.                                            |

| 12      | SDO/ALT ADDRESS | Serial Data Output/Alternate I <sup>2</sup> C Address Select.                                           |

| 13      | SDA/SDI/SDIO    | Serial Data (I <sup>2</sup> C)/Serial Data Input (SPI 4-Wire)/Serial Data Input and Output (SPI 3-Wire) |

| 14      | SCL/SCLK        | Serial Communications Clock.                                                                            |

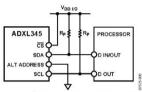

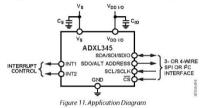

### SERIAL COMMUNICATIONS

I2C and SPI digital communications are available. In both cases, the ADXL345 operates as a slave. I²C mode is enabled if the  $\overline{\text{CS}}$  pin is tied high to VDD NO. The CS pin should always be tied high to  $V_{DD\, BO}$  or be driven by an external controller because there is no default mode if the  $\overline{CS}$  pin is left unconnected. Therefore, not taking these precautions may result in an inability to communicate with the part. In SPI mode, the CS pin is controlled by the bus master. In both SPI and I2C modes of operation, data transmitted from the ADXL345 to the master device should be ignored during writes to the ADXL345.

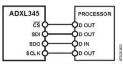

### SPI

For SPI, either 3- or 4-wire configuration is possible, as shown in the connection diagrams in Figure 3 and Figure 4. Clearing the SPI bit in the DATA\_FORMAT register (Address 0x31) selects 4-wire mode, whereas setting the SPI bit selects 3-wire mode. The maximum SPI clock speed is 5 MHz with 100 pF maximum loading, and the timing scheme follows clock polarity (CPOL) = 1 and clock phase (CPHA) = 1.

$\overline{\text{CS}}$  is the serial port enable line and is controlled by the SPI master. This line must go low at the start of a transmission and high at the end of a transmission, as shown in Figure 5. SCLK is the serial port clock and is supplied by the SPI master. It is stopped high when  $\overline{\text{CS}}$  is high during a period of no transmission. SDI and SDO are the serial data input and output, respectively. Data should be sampled at the rising edge of SCLK.

Figure 3. 3-Wire SPI Connection Diagram

Figure 4. 4-Wire SPI Connection Diagram

To read or write multiple bytes in a single transmission, the multiple-byte bit, located after the  $R/\overline{W}$  bit in the first byte transfer (MB in Figure 5 to Figure 7), must be set. After the register addressing and the first byte of data, each subsequent set of clock pulses (eight clock pulses) causes the ADXL345 to point to the next register for a read or write. This shifting continues until the clock pulses cease and  $\overline{\text{CS}}$  is deasserted. To perform reads or writes on different, nonsequential registers,  $\overline{\text{CS}}$  must be deasserted between transmissions and the new register must be addressed separately.

The timing diagram for 3-wire SPI reads or writes is shown in Figure 7. The 4-wire equivalents for SPI writes and reads are shown in Figure 5 and Figure 6, respectively.

Table 8. SPI Digital Input/Output Voltage

| Parameter                                   | Limit <sup>1</sup>        | Unit  |  |

|---------------------------------------------|---------------------------|-------|--|

| Digital Input Voltage                       |                           |       |  |

| Low Level Input Voltage (VIL)               | 0.2 × V <sub>DD I/O</sub> | V max |  |

| High Level Input Voltage (V <sub>IH</sub> ) | 0.8 × V <sub>DD I/O</sub> | V min |  |

| Digital Output Voltage                      |                           |       |  |

| Low Level Output Voltage (Vol)              | $0.15 \times V_{DD1/0}$   | V max |  |

| High Level Output Voltage (VoH)             | 0.85 × VDD1/0             | V min |  |

<sup>1</sup> Limits based on characterization results, not production tested.

| Table 9. SPI | Timing (TA | = 25°C, | $V_s = 2.5$ | $V, V_{DDIO}$ | $= 1.8 \text{ V})^{1}$ |

|--------------|------------|---------|-------------|---------------|------------------------|

|              |            |         |             | $\neg$        |                        |

|                    | Limit <sup>2, 3</sup> |     |      |                                                                               |  |  |

|--------------------|-----------------------|-----|------|-------------------------------------------------------------------------------|--|--|

| Param eter         | Min                   | Max | Unit | Description                                                                   |  |  |

| fsclk              |                       | 5   | MHz  | SPI clock frequency                                                           |  |  |

| tsclk              | 200                   |     | ns   | 1/(SPI clock frequency) mark-space ratio for the SCLK input is 40/60 to 60/40 |  |  |

| t <sub>DELAY</sub> | 10                    |     | ns   | CS falling edge to SCLK falling edge                                          |  |  |

| tquiet             | 10                    |     | ns   | SCLK rising edge to CS rising edge                                            |  |  |

| tois               | 1775                  | 100 | ns   | CS rising edge to SDO disabled                                                |  |  |

| tcs,pis            | 250                   |     | ns   | CS deassertion between SPI communications                                     |  |  |

| ts                 | 0.4 × tsa.k           |     | ns   | SCLK low pulse width (space)                                                  |  |  |

| tm                 | $0.4 \times t_{SCLK}$ |     | ns   | SCLK high pulse width (mark)                                                  |  |  |

| tspo               |                       | 95  | ns   | SCLK falling edge to SDO transition                                           |  |  |

| <b>t</b> SETUP     | 10                    |     | ns   | SDI valid before SCLK rising edge                                             |  |  |

| THOLD              | 10                    |     | ns   | SDI valid after SCLK rising edge                                              |  |  |

$<sup>^1</sup>$  The  $^{12}$ S, SCLK, SDI, and SDO pins are not internally pulled up or down; they must be driven for proper operation.  $^1$  Limits based on characterization results, characterized with  $_{150x}$  = 5 MHz and bus load capacitance of 100 pF; not production tested.  $^3$  The timing values are measured corresponding to the input thresholds ( $^{12}$ C and  $^{13}$ C) in Table 8.

### $I^2C$

With  $\overline{\text{CS}}$  tied high to V<sub>DD VO</sub>, the ADXL345 is in I<sup>2</sup>C mode, requiring a simple 2-wire connection as shown in Figure 8. The ADXL345 conforms to the *UM10204 PC-Bus Specification and User Manual*, Rev. 03—19 June 2007, available from NXP Semiconductor. It supports standard (100 kHz) and fast (400 kHz) data transfer modes if the timing parameters given in Table 11 and Figure 10 are met. Single- or multiple-byte reads/writes are supported, as shown in Figure 9. With the SDO/ALT ADDRESS pin high, the 7-bit I<sup>2</sup>C address for the device is 0x1D, followed by the R/W bit. This translates to 0x3A for a write and 0x3B for a read. An alternate I<sup>2</sup>C address of 0x53 (followed by the R/W bit) can be chosen by grounding the SDO/ALT ADDRESS pin (Pin 12). This translates to 0xA6 for a write and 0xA7 for a read.

If other devices are connected to the same I²C bus, the nominal operating voltage level of these other devices cannot exceed  $V_{\rm DD\,IO}$  by more than 0.3 V. External pull-up resistors,  $R_{\rm P}$  are necessary for proper I²C operation. Refer to the UM10204~FC-Bus Specification and User Manual, Rev. 03—19 June 2007, when selecting pull-up resistor values to ensure proper operation.

Table 10. I<sup>2</sup>C Digital Input/Output Voltage

| Parameter                                   | Limit <sup>1</sup>         | Unit  |  |

|---------------------------------------------|----------------------------|-------|--|

| Digital Input Voltage                       |                            |       |  |

| Low Level Input Voltage (VIL)               | 0.25 × V <sub>DD I/O</sub> | V max |  |

| High Level Input Voltage (V <sub>IH</sub> ) | 0.75 × V <sub>DD I/O</sub> | V min |  |

| Digital Output Voltage                      |                            |       |  |

| Low Level Output Voltage (Vol.)2            | 0.2 × V <sub>DD I/O</sub>  | V max |  |

$^1$  Limits based on characterization results; not production tested.  $^2$  The limit given is only for  $V_{\text{DOM}}$  <2 V. When  $V_{\text{DOM}}$  > 2 V, the limit is 0.4 V max.

Figure 8. FC Connection Diagram (Address 0x53)

| SINGLE-BYTE WRITE   |                     |                  | _   |                      | _        |      |      |      |      |          |

|---------------------|---------------------|------------------|-----|----------------------|----------|------|------|------|------|----------|

| MASTER START SL     | AVE ADDRESS + WRITE | REGISTER ADDRESS |     | DATA                 |          | STOP |      |      |      |          |

| SLAVE               | AC                  | К                | ACK |                      | ACK      |      |      |      |      |          |

| MULTIPLE BYTE WRITE |                     |                  |     |                      |          |      |      |      |      |          |

| MASTER START SL     | AVE ADDRESS + WRITE | REGISTER ADDRESS |     | DATA                 |          | DATA |      | STOP |      |          |

| SLAVE               | AC                  | К                | ACK |                      | ACK      |      | ACK  |      |      |          |

| SINGLE BYTE READ    |                     |                  |     | •                    |          |      |      |      |      |          |

| MASTER START SL     | AVE ADDRESS + WRITE | REGISTER ADDRESS |     | START   SLAVE ADDRES | S + READ |      |      | NACK | STOP |          |

| SLAVE               | AC                  | K                | ACK | 255000               |          | ACK  | DATA | · ·  |      |          |

| MULTIPLE BYTE READ  |                     | /t.              | 70  | 8                    |          | 2000 |      | - 50 | 100  |          |

| MASTER START SI     | AVE ADDRESS + WRITE | REGISTER ADDRESS | 1 3 | START! SLAVE ADDRES  | S + READ |      |      | ACK  |      | NACK STO |

| SLAVE               | AC                  | К                | ACK |                      |          | ACK  | DATA | 3    | DATA |          |

THIS START IS EITHER A RESTART OR A STOP FOLLOWED BY A START.

NOTES

1. THE SHADED AREAS REPRESENT WHEN THE DEVICE IS LISTENING.

Figure 9. FC Device Addressing

Table 11.  $I^2C$  Timing  $(T_A = 25^{\circ}C, V_S = 2.5 \text{ V}, V_{DD 1/0} = 1.8 \text{ V})$

|                     |            | Limit <sup>1, 2</sup> |      |                                                                                 |

|---------------------|------------|-----------------------|------|---------------------------------------------------------------------------------|

| Parameter Parameter | Min        | Max                   | Unit | Description                                                                     |

| f <sub>SCL</sub>    |            | 400                   | kHz  | SCL clock frequency                                                             |

| t <sub>1</sub>      | 2.5        |                       | μs   | SCL cycle time                                                                  |

| t <sub>2</sub>      | 0.6        |                       | μs   | thigh, SCL high time                                                            |

| t <sub>3</sub>      | 1.3        |                       | μs   | t <sub>LOW</sub> , SCL low time                                                 |

| t <sub>4</sub>      | 0.6        |                       | μs   | t <sub>HD, STAr</sub> start/repeated start condition hold time                  |

| <b>t</b> 5          | 350        |                       | ns   | tsu, data setup time                                                            |

| t63, 4, 5, 6        | 0          | 0.65                  | μs   | thd, data hold time                                                             |

| t <sub>7</sub>      | 0.6        |                       | μs   | tsu, sta, setup time for repeated start                                         |

| ts                  | 0.6        |                       | μs   | tsu, stop condition setup time                                                  |

| t <sub>9</sub>      | 1.3        |                       | μs   | t <sub>BUF</sub> , bus-free time between a stop condition and a start condition |

| t <sub>10</sub>     |            | 300                   | ns   | t <sub>B</sub> , rise time of both SCL and SDA when receiving                   |

|                     | 0          |                       | ns   | ts, rise time of both SCL and SDA when receiving or transmitting                |

| t <sub>11</sub>     |            | 250                   | ns   | t <sub>F</sub> , fall time of SDA when receiving                                |

|                     |            | 300                   | ns   | t <sub>F</sub> , fall time of both SCL and SDA when transmitting                |

|                     | 20 + 0.1 C | b <sup>7</sup>        | ns   | t <sub>F</sub> , fall time of both SCL and SDA when transmitting or receiveing  |

| Cb                  |            | 400                   | pF   | Capacitive load for each bus line                                               |

Figure 10. FCTiming Diagram

Limits based on characterization results, with fs2 = 400 kHz and a 3 mA sink current; not production tested.

All values referred to the Vs and the Vs, levels given in Table 10.

Is is the data hold time that is measured from the falling edge of SCL. It applies to data in transmission and acknowledge times.

A transmitting device must internally provide an output hold time of at least 300 ns for the SDA signal (with respect to Vstance) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

The maximum ty alue must be met only if the device does not stretch the low period (ts) of the SCL signal.

The maximum value for ts is a function of the dock low time (ts), the dock rise time (ts), and the minimum data setup time (ts), this value is calculated as ts/maximum to the top to the school capacitance of one bus line in picofarads.

### APPLICATIONS INFORMATION

### POWER SUPPLY DECOUPLING

A 1  $\mu F$  tantalum capacitor ( $C_0$ ) at  $V_0$  and a 0.1  $\mu F$  ceramic capacitor ( $C_{10}$ ) at  $V_{DD\ \nu 0}$  placed close to the ADXL345 supply pins is used for testing and is recommended to adequately decouple the accelerometer from noise on the power supply. If additional decoupling is necessary, a resistor or ferrite bead, no larger than 100  $\Omega$ , in series with  $V_0$  may be helpful. Additionally, increasing the bypass capacitance on  $V_0$  to a 10  $\mu F$  tantalum capacitor in parallel with a 0.1  $\mu F$  ceramic capacitor may also improve noise.

Care should be taken to ensure that the connection from the ADXL345 ground to the power supply ground has low impedance because noise transmitted through ground has an effect similar to noise transmitted through  $V_{\rm S}$ . It is recommended that  $V_{\rm S}$  and  $V_{\rm DD\,IFO}$  be separate supplies to minimize digital clocking noise on the  $V_{\rm S}$  supply. If this is not possible, additional filtering of the supplies as previously mentioned may be necessary.

### MECHANICAL CONSIDERATIONS FOR MOUNTING

The ADXL345 should be mounted on the PCB in a location close to a hard mounting point of the PCB to the case. Mounting the ADXL345 at an unsupported PCB location, as shown in Figure 12, may result in large, apparent measurement errors due to undampened PCB vibration. Locating the accelerometer near a hard mounting point ensures that any PCB vibration at the accelerometer is above the accelerometer's mechanical sensor resonant frequency and, therefore, effectively invisible to the accelerometer.

Figure 12. Incorrectly Placed Accelerometers

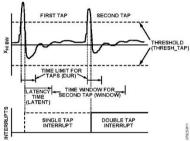

### TAP DETECTION

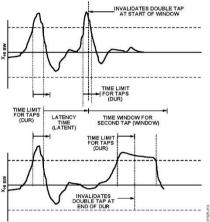

The tap interrupt function is capable of detecting either single or double taps. The following parameters are shown in Figure 13 for a valid single and valid double tap event:

The tap detection threshold is defined by the THRESH\_TAP register (Address 0x1D).

- The maximum tap duration time is defined by the DUR register (Address 0x21).

- The tap latency time is defined by the latent register (Address 0x22) and is the waiting period from the end of the first tap until the start of the time window, when a second tap can be detected, which is determined by the value in the window register (Address 0x23).

- The interval after the latency time (set by the latent register) is defined by the window register. Although a second tap must begin after the latency time has expired, it need not finish before the end of the time defined by the window register.

Figure 13. Tap Interrupt Function with Valid Single and Double Taps

If only the single tap function is in use, the single tap interrupt is triggered when the acceleration goes below the threshold, as long as DUR has not been exceeded. If both single and double tap functions are in use, the single tap interrupt is triggered when the double tap event has been either validated or invalidated.

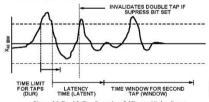

Several events can occur to invalidate the second tap of a double tap event. First, if the suppress bit in the TAP\_AXES register (Address 0x2A) is set, any acceleration spike above the threshold during the latency time (set by the latent register) invalidates the double tap detection, as shown in Figure 14.

Figure 14. Double Tap Event Invalid Due to High g Event When the Suppress Bit Is Set

A double tap event can also be invalidated if acceleration above the threshold is detected at the start of the time window for the second tap (set by the window register). This results in an invalid double tap at the start of this window, as shown in Figure 15. Additionally, a double tap event can be invalidated if an accel-

eration exceeds the time limit for taps (set by the DUR register), resulting in an invalid double tap at the end of the DUR time limit for the second tap event, also shown in Figure 15.

Figure 15. Tap Interrupt Function with Invalid Double Taps

Single taps, double taps, or both can be detected by setting the respective bits in the INT\_ENABLE register (Address 0x2E). Control over participation of each of the three axes in single tap/double tap detection is exerted by setting the appropriate bits in the TAP\_AXES register (Address 0x2A). For the double tap function to operate, both the latent and window registers must be set to a nonzero value.

Every mechanical system has somewhat different single tap/double tap responses based on the mechanical characteristics of the system. Therefore, some experimentation with values for the latent, window, and THRESH\_TAP registers is required. In general, a good starting point is to set the latent register to a value greater than 0x10, to set the window register to a value greater than 0x10, and to set the THRESH\_TAP register to be greater than 3 g. Setting a very low value in the latent, window, or THRESH\_TAP register may result in an unpredictable response due to the accelerometer picking up echoes of the tap inputs.

After a tap interrupt has been received, the first axis to exceed the THRESH\_TAP level is reported in the ACT\_TAP\_STATUS register (Address 0x2B). This register is never cleared, but is overwritten with new data.

### THRESHOLD

The lower output data rates are achieved by decimating a common sampling frequency inside the device. The activity, free-fall, and single tap/double tap detection functions are performed using unfiltered data. Since the output data is filtered, the high frequency and high g data that is used to

determine activity, free-fall, and single tap/double tap events may not be present if the output of the accelerometer is examined. This may result in trigger events being detected when acceleration does not appear to trigger an event because the unfiltered data may have exceeded a threshold or remained below a threshold for a certain period of time while the filtered output data has not exceeded such a threshold.

### LINK MODE

The function of the link bit is to reduce the number of activity interrupts that the processor must service by setting the device to look for activity only after inactivity. For proper operation of this feature, the processor must still respond to the activity and inactivity interrupts by reading the INT\_SOURCE register (Address 0x30) and, therefore, clearing the interrupts. If an activity interrupt is not cleared, the part cannot go into autosleep mode. The asleep bit in the ACT\_TAP\_STATUS register (Address 0x2B) indicates if the part is asleep.

### SLEEP MODE VS. LOW POWER MODE

In applications where a low data rate is sufficient and low power consumption is desired, it is recommended that the low power mode be used in conjunction with the FIFO. The sleep mode, while offering a low data rate and low average current consumption, suppresses the DATA\_READY interrupt, preventing the accelerometer from sending an interrupt signal to the host processor when data is ready to be collected. In this application, setting the part into low power mode (by setting the LOW\_POWER bit in the BW\_RATE register) and enabling the FIFO in FIFO mode to collect a large value of samples reduces the power consumption of the ADXL345 and allows the host processor to go to sleep while the FIFO is filling up.

### USING SELF-TEST

The self-test change is defined as the difference between the acceleration output of an axis with self-test enabled and the acceleration output of the same axis with self-test disabled (see Endnote 4 of Table 1). This definition assumes that the sensor does not move between these two measurements, because if the sensor moves, a non-self-test related shift corrupts the test.

Proper configuration of the ADXL345 is also necessary for an accurate self-test measurement. The part should be set with a data rate greater than or equal to 100 Hz. This is done by ensuring that a value greater than or equal to 0x0A is written into the rate bits (Bit D3 through Bit D0) in the BW\_RATE register (Address 0x2C). It is also recommended that the part be set to full-resolution, 16 g mode to ensure that there is sufficient dynamic range for the entire self-test shift. This is done by setting Bit D3 of the DATA\_FORMAT register (Address 0x31) and writing a value of 0x03 to the range bits (Bit D1 and Bit D0) of the DATA\_FORMAT register (Address 0x31). This results in a high dynamic range for measurement and a 3.9 mg/LSB scale factor.

After the part is configured for accurate self-test measurement, several samples of x-, y-, and z-axis acceleration data should be retrieved from the sensor and averaged together. The number of

samples averaged is a choice of the system designer, but a recommended starting point is 0.1 sec worth of data, which corresponds to 10 samples at 100 Hz data rate. The averaged values should be stored and labeled appropriately as the self-test disabled data, that is, X<sub>T\_OPF</sub>, Y<sub>T\_OPF</sub>, and Z<sub>T\_OPF</sub>.

Next, self-test should be enabled by setting Bit D7 of the DATA\_FORMAT register (Address 0x31). The output needs some time (about four samples) to settle after enabling self-test. After allowing the output to settle, several samples of the x-, y-, and z-axis acceleration data should be taken again and averaged. It is recommended that the same number of samples be taken for this average as was previously taken. These averaged values should again be stored and labeled appropriately as the value with self-test enabled, that is, X<sub>ST\_ON</sub>, Y<sub>ST\_ON</sub>, and Z<sub>ST\_ON</sub>. Self-test can then be disabled by clearing Bit D7 of the DATA\_FORMAT register (Address 0x31).

With the stored values for self-test enabled and disabled, the self-test change is as follows:

$X_{ST} = X_{ST\_ON} - X_{ST\_OFF}$

$Y_{ST} = Y_{ST\_OPP} - Y_{ST\_OPP}$

$Z_{ST} = Z_{ST\_ON} - Z_{ST\_OPF}$

Because the measured output for each axis is expressed in LSBs,  $X_{\text{ST}}$ ,  $Y_{\text{ST}}$ , and  $Z_{\text{ST}}$  are also expressed in LSBs. These values can be converted to g's of acceleration by multiplying each value by the 3.9 mg/LSB scale factor, if configured for full-resolution, 16 g mode. Additionally, Table 12 through Table 15 correspond to the self-test range converted to LSBs and can be compared with the measured self-test change. If the part was placed into fullresolution,  $16\,g$  mode, the values listed in Table 12 should be used. Although the fixed 10-bit mode or a range other than  $16\,g$  can be used, a different set of values, as indicated in Table 13 through Table 15, would need to be used. Using a range below 8 g may result in insufficient dynamic range and should be considered when selecting the range of operation for measuring self-test. In addition, note that the range in Table 1 and the values in Table 12through Table 15 take into account all possible supply voltages, V<sub>s</sub>, and no additional conversion due to  $V_{\delta}$  is necessary.

If the self-test change is within the valid range, the test is considered successful. Generally, a part is considered to pass if the minimum magnitude of change is achieved. However, a part that changes by more than the maximum magnitude is not necessarily a failure.

### ADXL345

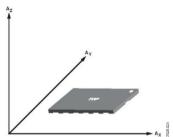

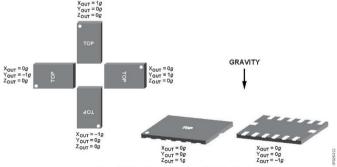

### **AXES OF ACCELERATION SENSITIVITY**

Figure 16. Axes of Acceleration Sensitivity (Corresponding Output Voltage Increases When Accelerated Along the Sensitive Axis)

Figure 17. Output Response vs. Orientation to Gravity

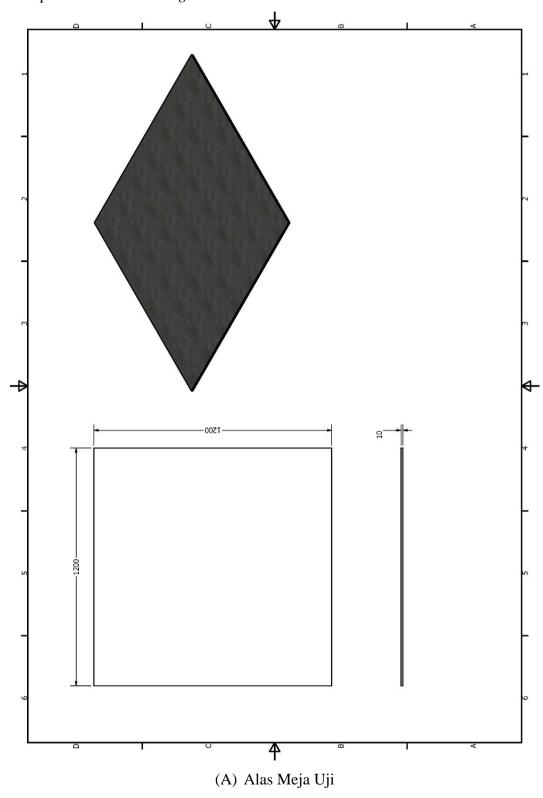

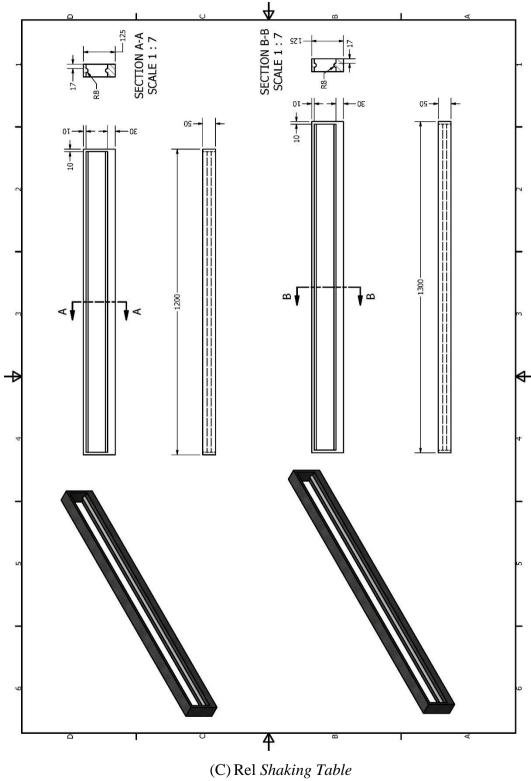

(B) Support (Penyangga) Alas Shaking Table

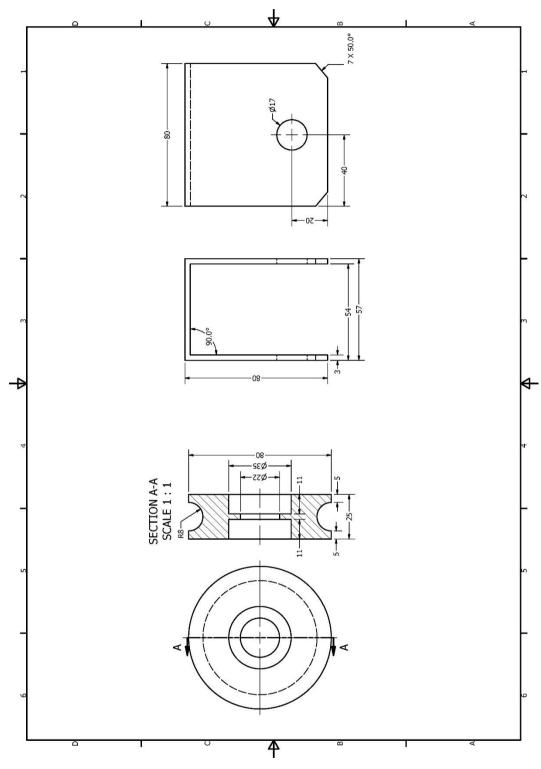

(D) Roda Shaking Table